|

|

|

|

|

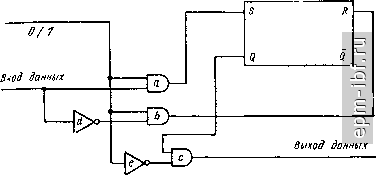

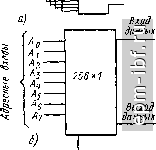

Главная Кремниевые микросхемы 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 [ 33 ] 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 могут быть организованы одним из следующих двух способов. Первый способ состоит в том, что каждая отдельная элементарная ячейка памяти адресуется индивидуально, что означает, что в нее отдельно может быть записана и из нее может быть считана информация (организация с поразрядной выборкой информации). При другом способе для адресации выделяется вполне опре- Чтение/запись  Рис. 8.1. Схема управления элементом памяти деленное, жестко фиксированное число элементарных ячеек, в которые может одновременно записываться и из которых одновременно считываться определенная порция информации (организация с пословной выборкой информации). Типовые полупроводниковые микросхемы памяти могут содержать от 256 до 16 384 отдельных двоичных элементов для хранения информации в одном корпусе с двухрядным расположением выводов. Как было показано ранее, триггер может использоваться в качестве временного элементарного запоминающего устройства в регистрах; посмотрим, как он может использоваться в качестве элемента памяти в ОЗУ. Известно, что каждый элемент памяти-это обычный /?5-триггер. На рис. 8.1 показаны логические цепи управления таким элементом, имеющиеся в любой микросхеме памяти. С их помощью путем подачи соответствующих входных сигналов можно либо посылать данные в триггер для записи, либо производить выборку информации из него. ВховЩ Z5BXI Рис. 8.2. Память объемом 256 8-разрядных слов- а - схе.ма соединения микросхем с поразрядной выборкой информации, б ~ схемное обозначение такой микросхемы- ZSBxt 156x1 BxadD 2561 Z5B-<1 ZSSxl Рассмотрим, как работает схема управления элементом памяти, Вкад1>2 изображенная на рис. 8.1. Если в Выход Л и^-в управления чтение/запись 2- появился положительный потенциал то он поступит на один из входов каждого из двух элементов И (элементов а и &). Поэтому, Выход Из в это же самое время в ли- - НИИ передачи данных имеется сигнал то на выходе элемента а BKodDii также появится сигнал Ь^., а на -~ выходе элемента b будет сформи- ВыхааЩ рован нулевой сигнал, так как схема НЕ (элемент d), реализующая ВходВк операцию отрицания, изменит зна- * чение сигнала 1 иа значение 0. Выходи Следовательно, на входе, уста- - навливающем триггер в состояние 1 (на входе S), появится сигнал ВходТ) U+, а на входе, устанавливающем - триггер в состояние О (на входе ВыхпЗВ - нулевой сигнал. В результате триггер окажется усгановлен-ВходИ состояние 1 и будет хра- нить логическую 1. В течение все-ВыхадНу го режима записи сигнал в канале - управления чтение/запись, соответствующий логической 1, инверти-)уется элементом НЕ (элементе). 1оэтому выход Q триггера оказывается заблокированным с помощью схемы И (элемент с), на нижнем входе которой присутствует нулевой сигнал. Аналогично, если в линии передачи данных появится нулевой сигнал, а сигнал в канале управления чтение/запись будет тем же самым (соответствующим режиму записи), триггер установится в состояние О и будет его сохранять. Чтобы можно было считать информацию из элемента памяти, в управляющем канале чтение/запись должен установиться сигнал 0. При этом заблокируются две схемы И (элементы а и 6), предохранив тем самым данные от нежелательных изменений в процессе считывания, и откроется схема совпадения с, на нижнем входе которой появится сигнал 1 после инвертирования элементом е нулевого сигнала  Чтение/запись в канале управления, На выходе элемента с появится сигнал, равный по значению сигналу на выходе Q триггера, т. е. сигнал, соответствующий логической 1, если триггер установлен в состояние 1, и нулевой сигнал в противном случае (когда триггер ие установлен в состояние 1 и Q = 0). В большинстве случаев традиционные микро-ЭВМ имеют 8-разрядные шины данных. Поэтому в каждой ад- Адресные! I - ° Rvnffu \ I- -JJ9 Входы данных , Выходи данных Чтение/запись >Si/XOdif Рис. 8.3. Память объемом 256 8-разрядных слов; а -схема соединения двух микросхем с пословной выборкой информации; б - схемное обозначение такой микросхемы ресуемой (не элементарной) ячейке памяти должны храниться 8-разрядные порции информации (8-разрядные слова). Для этой цели потребуется восемь микросхем, линии передачи адреса которых будут запараллелены (как это показано на рис. 8.2, а), если для организации памяти микро-ЭВМ воспользоваться микросхемами с поразрядной выборкой информации. Отдельные выходы данных (8-разрядного слова) Dj, De, D5, D4, D3, D2, Di, Dq (так же, как и входы) выбираются по одному из каждой микросхемы (рис. 8.2,6). Если каждая микросхема содержит 256 элементарных ячеек (элементов) памяти, получим общий объем памяти 256 слов, по восемь разрядов каждое, что потребует при адресации восемь адресных линий (отЛоДоЛ?). Если бы каждая микросхема содержала 1024 элемента памяти, это дало бы 1 Кбайт памяти, т. е. 1024 8-разрядных слова, и потребовало бы десять адресных линий (от Ло до Лэ). Вместо этого можно было бы воспользоваться микросхемами памяти с пословной выборкой информации и соединить их подобным образом. В этом случае получилась бы схема памяти (представленная на рис. 8.3, а) то- |

|

© 2007 EPM-IBF.RU

Копирование материалов разрешено в случае наличия письменного разрешения |