|

|

|

|

|

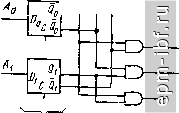

Главная Кремниевые микросхемы 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 [ 36 ] 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 Если иа линии выхода данных появится сигнал U+, а сигнал иа управляющем входе ПВ не изменится {U+), то р-канальный МОП-транзистор будет открыт, а я-канальный МОП-транзистор заперт. Следовательно, выход буфера получит положительный потенциал U+, Если в какой-либо момент времени сигнал на управляющем входе ПВ станет нулевым, то будет совершенно безразлично, какой сигнал присутствует в этот момент на линии выхода данных. На выходе элемента а в этом случае будет положительный потенциал У^, а на выходе элемента 6 нулевой. Поэтому оба МОП-транзистора будут заперты. Сопротивление запертого полевого МОП-транзистора, как отмечалось в гл. 1, составляет около миллиона миллионов ом (102), поэтому его выход практически можно считать отсоединенным от шины данных. Как работают адресные дешифраторы? Применение двоичной адресации обусловлено тем, что это сокращает число необходимых внешних линий адресов. Например, 10-канальный двоичный адресный вход в микросхему памяти позволяет определить 1024 различных адреса в этой микросхеме. Когда двоичный адрес через адресную шину попадает в микросхему памяти, его необходимо дешифрировать, чтобы обеспечить формирование правильных сигналов выбора требуемых строки и столбца в матрице памяти. Дешифрирование выполняется довольно просто с помощью схемы из логических элементов, подобной той, которая использовалась при формировании сигналов для отпирающих входов микросхем (см. рис. 8.5). В микросхеме памяти адрес, как правило, прежде всего подается на триггерный регистр, что позволяет произвести фиксацию сигналов адреса для дальнейшего его использования (адрес может быть предостанлен дешифратору в течение более длительного промежутка времени по сравнению со временем его нахождения в адресной шике). Кроме того, на инверсных выходах Qj регистра можно получить обратный код адреса. Микросхемы памяти, не содержащие триггерных регистров для приема адресных сигналов, должны иметь дополнительные элементы НЕ для формирования инверсных сигналов, используемых дешифратором кода адреса. Рассмотрим в качестве примера простой случай адресации матрицы памяти размерности 4X4 (четыре строчки и четыре столбца) с 16 двоичными ячейками памяти. Для этого потребуются два адресных входа для получе- Выход 1 Виход 2  Выход J ния четырех кодов адресов строк: 00, 01, 10, 11 и два адресных входа для получения аналогичных кодов адресов столбцов. Все это позволит произвести адресацию 16 1-разрядных ячеек памяти. Сигналы выбора строки и столбца могут быть получены дешифрированием двоичных адресных кодов схемой, представленной на рис. 8.74 Связи тактового генератора с адресным регистром на схеме не показаны. Тактовые импульсы .можно передавать по цепям управления таким образом, чтобы они подавались на регистр только тогда, когда требуется изменить хранящийся в нем адрес. Схема на рис. 8.7 работает так же, как и ранее описанная схема формирования сигналов для отпирающих входов микросхем (см. рнс. 8.5). Можно встретить и другие схемы дешифраторов, выполненные с применением различных логических элементов. Например, в микросхеме памяти 5101 используются элементы И для дешифрирования строки и элементы ИЛИ-НЕ для дешифрирования 3-разрядного адреса одного из восьми столбцов. Ранее упоминалось о сигналах выбора микросхемы памяти. Они используются в цепях включения адресных дешифраторов тех микросхем, которые выбраны. Рггистр адреса Рис. 8.7. Схема двухвходового дешифратора адреса Что подразумевается под памятью статической, динамической и памятью, не сохраняющей информацию при отключении напряжения питания? Память, о которой до сих пор шла речь, предназначена для хранения информации, не нуждающейся в непрерывном обновлении, и поэтому она называется статической. Кроме того, эта память характеризуется еще и тем. Как следует из этой схемы, дешифратор является преобразователем двоичного кода в код один из п , под которым подразумевается п-разрядный код, каждая кодовая комбинация которого содержит одну единищ и п-\ нулей. {Прим. пер.) что хранимая в Ней информация теряется при выключении напряжения питания. Поэтому эта память относится к памяти, не сохраняющей информацию при отключении напряжения питания, или непостоянной памяти (volatile memory). Наиболее распространенным элементом ОЗУ является микросхема 2102 с 16 выводами, в корпусе с двухряд- Рис. 8.8. Базовая ячейка микросхемы памяти 2102, представляющая собой триггер из двух инвертирующих п-МОП-ключей /72 U Нагрузки ным расположением выводов, с объемом памяти 1024X1 двоичных разрядов, изготовленная по га-МОП-технологии. В ней для хранения информации используются схемы из л-МОП-транзисторов с перекрестным соединением, причем каждая элементарная ячейка состоит из четырех таких транзисторов (рис. 8.8). Данные хранятся в виде положительных зарядов на затворах транзисторов либо <5з, либо Q4, что и приводит к отпиранию соответствующего МОП-транзистора. Транзисторы Qi и Q2 имеют повышенное сопротивление по сравнению с обычным МОП-транзистором и используются в схеме как нагрузки. Предположим, что транзистор Q3 открыт, т. е. на его затворе сохраняется положительный заряд. Через поддерживаемый в открытом состоянии транзистор Qi ток может протекать к земле В связи с этим потенциал на входе I близок к нулю. (Действительное его значение зависит от состояния сопротивлений проводящих транзисторов Qi и Qj). Следовательно, потенциал затвора транзистора Q4 нулевой или близок к нулю, н, таким образом, транзистор заперт. Заряд на затворе транзистора Q3 поддерживается транзистором Q2 путем возмещения той части заряда, которая могла бы стечь. Поэтому ячейка памяти остается в том же логическом состоянии до момента, пока оно не сменится в результате новой записи. Все это остается в силе и в случае, когда транзистор Q4 открыт, а Q3 заперт. Другой распространенный тип ячейки ОЗУ - это ячейка дина.мического ОЗУ, в которой данные хранятся в виде зарядов конденсатора. На рис. 8.9 приведена схема ячейки динамической памяти на трех га-МОП-транзисторах. |

|

© 2007 EPM-IBF.RU

Копирование материалов разрешено в случае наличия письменного разрешения |